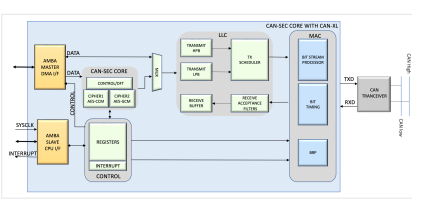

CAN-SEC Acceleration Engine

Arasan’s CAN-SEC Acceleration Engine core is easy to integrate with the Host processor using AMBA-APB, AHB_Lite or AMBA-AXI standard interface. This highly configurable design supports programmable Interrupts, data and baud rates, acceptance filters & buffering schemes specific to the application.

View CAN-SEC Acceleration Engine full description to...

- see the entire CAN-SEC Acceleration Engine datasheet

- get in contact with CAN-SEC Acceleration Engine Supplier

Block Diagram of the CAN-SEC Acceleration Engine IP Core

Video Demo of the CAN-SEC Acceleration Engine IP Core

Arasan, a leading provider of semiconductor IP for all things mobile, including automobiles released its 2’nd generation of CAN IP FPGA demo video.