Compact, low-power 32-bit RISC CPU

The cacheless memory architecture of the eSi-3200 allows for deterministic performance, making it particularly suitable for hard real-time control applications. It uses a modified-Harvard memory architecture allowing for simultaneous instruction and data fetch. The 5-stage pipeline allows GHz clock frequencies to be achieved.

The eSi-3200’s instruction set includes everything you would expect in a high-performance processor. There are a number of optional application specific instructions and addressing modes. A set of IEEE-754 compliant single-precision floating point instructions are available. Integer arithmetic instructions include a full 64 multiply and accumulate and divide. Bit manipulation instructions such as bitfield extract and insert, count leading zeros, population count, find first set and bit reverse can be included. Integer square root, absolute value, min/max, CRC and parity are also available. 32-bit SIMD instructions with 16-bit elements exploit data parallelism and reduce loop counts. Wait-for-interrupt instructions allow fast entry to low power states, enabling clock and power gating.

For those applications that require extreme performance or ultra low power operation, user-defined instructions and registers can be implemented. Instructions are encoded in either 16 or 32-bits, with all of the commonly used instructions being encoded in 16-bits, maximizing code density and minimizing instruction fetch power consumption.

The processor supports both user and supervisor operating modes, with privileged instructions and memory areas via the optional MPU, to allow an O/S kernel to be fully protected from user applications.

Hardware debug facilities include hardware breakpoints, watchpoints, trace, null pointer detection and single stepping for fast debugging of ROM, FLASH and RAM based programs.

View Compact, low-power 32-bit RISC CPU full description to...

- see the entire Compact, low-power 32-bit RISC CPU datasheet

- get in contact with Compact, low-power 32-bit RISC CPU Supplier

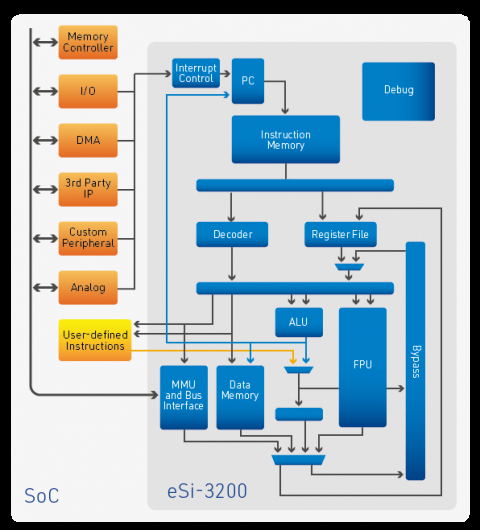

Block Diagram of the Compact, low-power 32-bit RISC CPU IP Core

RISC IP

- DSP-enhanced ARC EMxD and HS4xD processors provide combined RISC + DSP processing for computation intensive applications

- Ultra low power, high-performance DSP / controller RISC core

- 32-bit High Performance Single/Multicore RISC Processor

- 32-bit High Performance Single/Multicore RISC System-on-Chip

- 32-bit High Performance Single/Multicore RISC Processor with code compression

- 32-bit High Performance Single/Multicore RISC System-on-Chip with code compression