2.5D GPU / 2D & 3D Vector Graphics (OpenVG) Accelerator - D/AVE HD

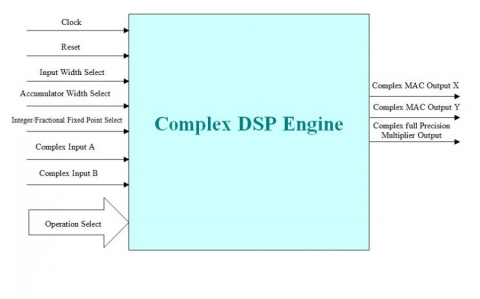

Complex DSP Engine Core

View Complex DSP Engine Core full description to...

- see the entire Complex DSP Engine Core datasheet

- get in contact with Complex DSP Engine Core Supplier

Block Diagram of the Complex DSP Engine Core IP Core

DSP IP

- High Performance Scalable Sensor Hub DSP Architecture

- Modern Audio DSP, designed for battery operated, high-performance, audio and voice applications

- Modern, high performance Audio DSP, optimized for far-field noise reduction and Artificial Intelligence speech recognition

- High-efficiency vector DSP cores for 5G and 5G-Advanced

- Tensilica Fusion F1 DSP

- Tensilica HiFi 5 DSP