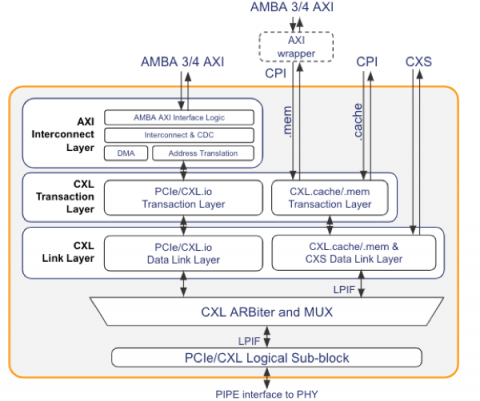

Rambus CXL 2.0 Controller with AXI is a parameterizable Compute Express Link (CXL) controller Soft IP designed for ASIC and FPGA implementation. Rambus CXL 2.0 Controller with AXI leverages PLDA's silicon proven PCIe 5.0 Controller architecture for the CXL.io path, and adds the CXL.cache and CXL.mem paths specific to CXL. The Controller supports the AMBA® AXI™ Protocol Specification for CXL.io traffic, and either Intel CXL-cache/mem Protocol Interface (CPI) or a AMBA® AXI™ Protocol Specification for CXL.mem and CPI interface for CXL.cache traffic, or the AMBA® CXS Protocol Specification. Rambus CXL 2.0 Controller with AXI also complies with the Intel PHY Interface for PCI Express (PIPE) specification version 5.x and supports the PIPE LPC and SERDES modes. The provided Graphical User Interface (GUI) Wizard allows designers to tailor the IP to their exact requirements, by enabling, disabling, and adjusting a vast array of parameters, including CXL device type, PIPE interface configuration, buffer sizes and latency, low power support, SR-IOV parameters, etc. for optimal throughput, latency, size and power. The Controller is extensively verified using commercial as well as homegrown VIP and testsuites, and has been integrated with a number of PCIe 5.0 PHY IP.