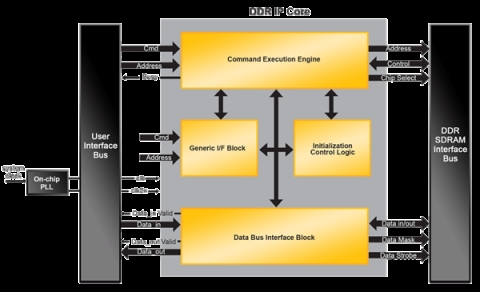

DDR SDRAM Controller - Non-Pipelined

The DDR SDRAM Controller is a parameterized core giving users the flexibility for modifying data widths, burst transfer rates and CAS latency settings in a design. In addition, the DDR core supports intelligent bank management, which is done by maintaining a database of "all banks activated" and the "rows activated" in each bank. With this information, the DDR SDRAM Controller decides if an active or pre-charge command is needed. This effectively reduces the latency of read/write commands issued to the DDR SDRAM.

View DDR SDRAM Controller - Non-Pipelined full description to...

- see the entire DDR SDRAM Controller - Non-Pipelined datasheet

- get in contact with DDR SDRAM Controller - Non-Pipelined Supplier

Block Diagram of the DDR SDRAM Controller - Non-Pipelined IP Core

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software