Dual Port Register File Compiler (1 Read-Only Port, 1 Write-Only Port)

Deinterlacer

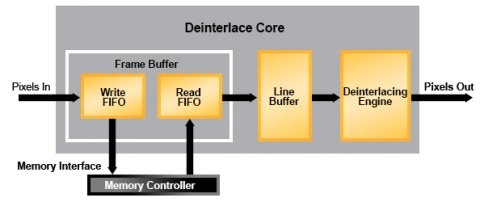

Interlaced video frames consists of two sequent fields, which are scanned at even and odd lines of the image sensor. Interlaced video has less transmission bandwidth, but most modern displays support progressive frame only. The two interlaced fields must be converted to one progressive frame for display, which is known as deinterlacing. As the two interlaced fields are taken at different time, there will be flicker and jagged edges in the combined frame. A good deinterlacing algorithm should reduce these artifacts as much as possible and provide good video quality in the process. Lattice Deinterlacer IP core provides several deinterlacing algorithms for different video quality and resource: weave, bob, intra and inter motion adaptive deinterlacing algorithms.

View Deinterlacer full description to...

- see the entire Deinterlacer datasheet

- get in contact with Deinterlacer Supplier

Block Diagram of the Deinterlacer IP Core

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software