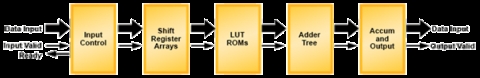

The Lattice Distributed Arithmetic Finite Impulse Response (DA-FIR) Filter Generator IP implements a highly configurable, multi-channel DA-FIR filter, using distributed arithmetic algorithms implemented in FPGA Look Up Table (LUT) or Embedded Block Memory (EBR) to efficiently support the sum-of-product calculations required to perform the filter function. These techniques generate very area-efficient utilization of the FPGA LUTs while enabling savings of multiply-accumulate blocks (sysDSP) for other design logic. As a result, the DA-FIR Filter Generator IP core is extremely useful for implementing custom DSP blocks in Lattice FPGAs. Please refer to the user's guide to determine which cores are available for each device family.