DPA- and FIA-resistant Ultra Low Power FortiCrypt AES IP core

This can be an ideal solution for battery-powered devices, which often work in a power-save mode and wake up from time to time for as-short-as-possible periods.

In addition, devices that do massive AES decrypt/encrypt operations can benefit from this IP core, by saving on electricity bills.

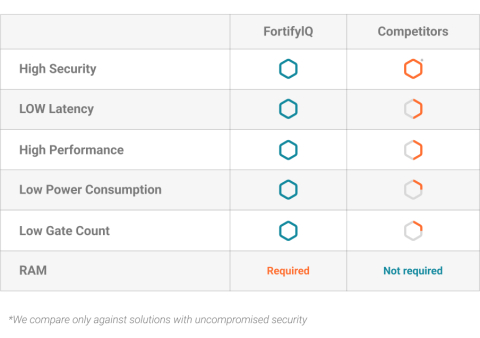

This is a unique solution in the market since it consumes significantly less power than other commercially available solutions.

The AES ULP-DPA-FIA IP Core, as well as all the FortiCrypt products, is based on RAMBAM - the next-generation purely algorithmic, implementation-agnostic protection scheme of AES. It is designed to provide the highest level of protection against side-channel attacks (SCA) and fault injection attacks (FIA) including SIFA.

The RAMBAM protection scheme utilizes masking methods based on finite field arithmetic that implement attack resistance without incurring extra latency costs.

The core protection mechanism was verified using the rigorous Test Vector Leakage Assessment (TVLA) test at 1B traces, both by FortifyIQ and by a third-party Common Criteria lab. Resistance to attacks was validated analytically and on a physical device. The cores are fully synthesizable and do not require custom cells or special place & route handling.

View DPA- and FIA-resistant Ultra Low Power FortiCrypt AES IP core full description to...

- see the entire DPA- and FIA-resistant Ultra Low Power FortiCrypt AES IP core datasheet

- get in contact with DPA- and FIA-resistant Ultra Low Power FortiCrypt AES IP core Supplier

Block Diagram of the DPA- and FIA-resistant Ultra Low Power FortiCrypt AES IP core

side channel IP

- Secure-IC Securyzr™ Tunable Cryptography solutions with embedded side-channel protections: AES - SHA2 - SHA3 - PKC - RSA - ECC - ML-KEM - ML-DSA - XMSS - LMS - SM2 - SM3 - SM4 - Whirlpool - CHACHA20 - Poly1305

- LPDDR4x/5 Secondary/Slave (memory side!) PHY

- LPDDR4x Secondary/Slave (memory side!) PHY

- LPDDR5 Secondary/Slave (memory side!) PHY

- LPDDR5X Secondary/Slave (memory side!) PHY

- Multi Protocol IO Concentrator (RDC) IP Core for Safe and Secure Ethernet Network