MIPI C-PHY v2.0 D-PHY v2.1 RX 2 trios/2 Lanes in TSMC (N5, N3E, N3P)

Dynamic Block Reed-Solomon Encoder

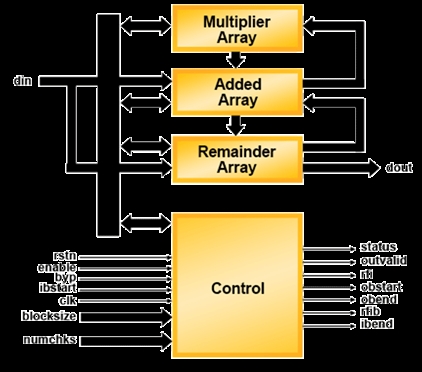

Reed-Solomon codes are written in the format RS(n,k) where k is the number of information symbols and n is the total number of symbols in a codeword or block. Each symbol in the codeword is wsymb bits wide. The first k symbols in the Reed-Solomon Encoder output are information symbols and the last n-k symbols are check symbols. This type of encoder, where the information symbols are unchanged and are followed by check symbols in the output, is called a systematic encoder. The figure below illustrates the operation of a systematic encoder.

View Dynamic Block Reed-Solomon Encoder full description to...

- see the entire Dynamic Block Reed-Solomon Encoder datasheet

- get in contact with Dynamic Block Reed-Solomon Encoder Supplier

Block Diagram of the Dynamic Block Reed-Solomon Encoder IP Core

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software