Software Defined Radio with Spread spectrum and SOQPSK for Telemetry applications

Ethernet MAC 10G/25G

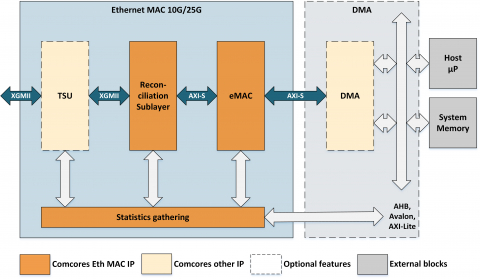

The Client-side interface is a 64-bit AXI-S and comes with a 64-bit XGMII interfaces on the PHY side. The Ethernet MAC IP features a compact and low latency solution, it is highly configurable and can optionally include IEEE 1588 Timestamping Unit (TSU). The Ethernet MAC IP is prepared for easy integration with Comcores Ethernet PCS 10G/25G IP solution.

View Ethernet MAC 10G/25G full description to...

- see the entire Ethernet MAC 10G/25G datasheet

- get in contact with Ethernet MAC 10G/25G Supplier

Block Diagram of the Ethernet MAC 10G/25G IP Core

Ethernet IP

- 10G-100G MACsec Security Module for Ethernet

- 224G Ethernet PHY in TSMC (N3E, N2P)

- 112G Ethernet PHY in TSMC (N7, N6, N5, N3P)

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency