Ethernet Real-Time Publish-Subscribe (RTPS) IP Core

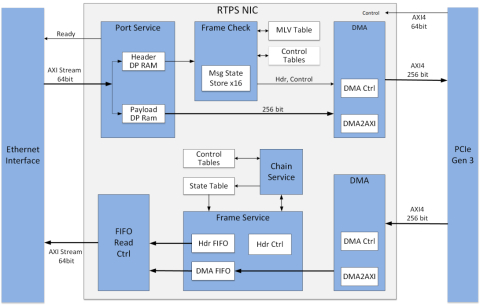

The core provides OMG DDSI-RTPS compliance, hardware-based message label filtering, hardware mapping of message label to host memory, and complete offload of RTPS handling including: Transmit messages, Receive messages, IEEE 1588 Precision Time Protocol (PTP), DMA controller, frame building/checking, and CRC generation/ checking.

The host interface to the core is AXI4. This allows the core to be connected to an external host processor over PCIe or to an embedded SoC processor. The core is built for dropping into an FPGA and providing the complete design from processor interface to Ethernet RTPS network interface.

This core is targeted towards applications in military/aerospace and has been implemented on AMD (Xilinx) UltraScale™/UltraScale+™ devices. The core comes with test benches, constraints and an example design, making design integration a straightforward task.

New Wave DV has a set of standard form factor boards featuring FPGAs, 10G Ethernet optics, and off-the-shelf reference designs for quick evaluation of the IP core.

View Ethernet Real-Time Publish-Subscribe (RTPS) IP Core full description to...

- see the entire Ethernet Real-Time Publish-Subscribe (RTPS) IP Core datasheet

- get in contact with Ethernet Real-Time Publish-Subscribe (RTPS) IP Core Supplier

Block Diagram of the Ethernet Real-Time Publish-Subscribe (RTPS) IP Core

Ethernet IP

- 10G-100G MACsec Security Module for Ethernet

- 224G Ethernet PHY in TSMC (N3E, N2P)

- 112G Ethernet PHY in TSMC (N7, N6, N5, N3P)

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency