Ethernet Switch / Router IP Core - Efficient and Massively Customizable

Packet Architects can provide IP cores with a full range of Ethernet switching and routing features such as IPv4/IPv6 routing, L2 switching, MPLS switching, advanced VLAN handling, classification, automatic learning etc.

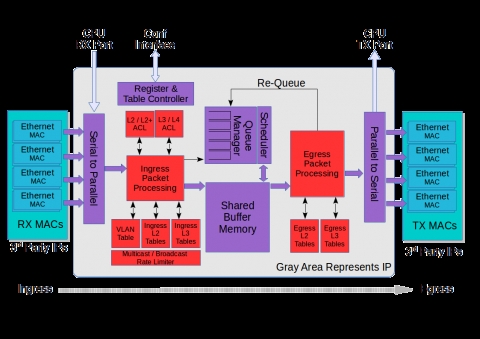

The core is built around a shared buffer memory architecture providing wire-speed switching and routing on all ports without head of line blocking. It offers dynamic allocation of packet buffers per port and priority to avoid starvation due to over-allocation. Advanced QoS features allow the most timing critical packets to get minimal delay while providing fairness between traffic classes.

No initial software setup is required and due to the hardware learning for MAC addresses the core is ready to receive and forward Ethernet frames immediately once powered up. There is a high performance processor interface for register configuration, and a high performance dedicated CPU port for slow path processing of packets.

The design is optimized for both FPGA and ASIC technology but does not have any dependencies on the underlying technology. If the target technology has TCAMs these can be utilized.

View Ethernet Switch / Router IP Core - Efficient and Massively Customizable full description to...

- see the entire Ethernet Switch / Router IP Core - Efficient and Massively Customizable datasheet

- get in contact with Ethernet Switch / Router IP Core - Efficient and Massively Customizable Supplier

Block Diagram of the Ethernet Switch / Router IP Core - Efficient and Massively Customizable

ethernet IP

- 10G-100G MACsec Security Module for Ethernet

- 224G Ethernet PHY in TSMC (N3E, N2P)

- 112G Ethernet PHY in TSMC (N7, N6, N5, N3P)

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency