Ceva-Waves Bluetooth 5.3 Low Energy Baseband Controller, software and profiles

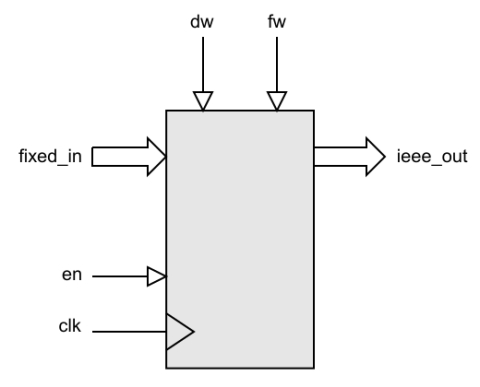

Fixed-point to Floating-point Converter

The design features a high-speed, fully pipelined architecture with a 2 clock-cycle latency.

View Fixed-point to Floating-point Converter full description to...

- see the entire Fixed-point to Floating-point Converter datasheet

- get in contact with Fixed-point to Floating-point Converter Supplier

Block Diagram of the Fixed-point to Floating-point Converter IP Core

IEEE 754 IP

- IEEE 754 Floating Point Coprocessor

- Single precision floating-point fast speed parametrized multi operands adder

- Single precision floating-point 2 cycle's multiplier

- Floating-point (IEEE 754) IP based on Arria 10 and Stratix 10 FPGAs

- Single precision, IEEE 754, floating point adder

- Single precision, IEEE 754, floating point multiplier