FlexNoC 5 Network-on-Chip (NoC)

With Arteris FlexNoC 5 interconnect IP, engineers achieve reduced wiring congestion, larger timing margins, and lower power consumption, as well as improved productivity and design quality through a set of intuitive and powerful development tools.

FlexNoC is the ideal interconnect for SoC designs requiring higher performance with minimum area and power. Its flexible architecture makes it the right solution for interconnects with both low latency requirements and high throughput needs. FlexNoC provides support for the additional features that today's SoCs require, such as clock domain conversion, width conversion, security, and multi-protocol support. The product supports the AMBA (APB, AHB, AXI) protocols and OCP and can easily be extended to support proprietary protocols.

View FlexNoC 5 Network-on-Chip (NoC) full description to...

- see the entire FlexNoC 5 Network-on-Chip (NoC) datasheet

- get in contact with FlexNoC 5 Network-on-Chip (NoC) Supplier

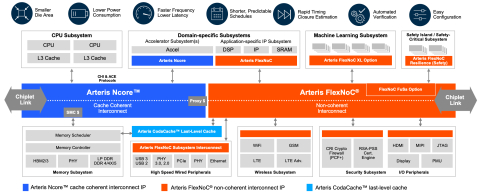

Block Diagram of the FlexNoC 5 Network-on-Chip (NoC) IP Core

Video Demo of the FlexNoC 5 Network-on-Chip (NoC) IP Core

Understanding how on-chip interconnect and DDR memory controller configurations impact the system performance, power and cost of multicore SoCs requires deep visibility. Sponsored by Synopsys and Arteris, this webinar illustrates how virtual prototyping tools and high-level architecture models provide SoC architects with the deep, system-level analysis they need to configure and optimize Quality-of-Service (QoS) features earlier in the design cycle.