GDDR6 PHY IP for 12nm

The GDDR6 OPHY utilizes state-of-the-art architecture in full custom analog mixed-signal design to overcome the problem of long-term impedance drift and clock phase drift, allowing impedance and clock phase updates without interrupting data traffic. The programmable timing PHY boundary combines flexibility with analog precision, and the result is ultra-low PHY read/write latency between OMC and the GDDR6 DRAM without sacrificing performance.

The GDDR6 OPHY was designed at the system level with minimal package substrate layer and PCB layer count in mind. This enables the integration of a GDDR6 memory sub-system solution in cost-sensitive applications, such as consumer edge devices, AI, GPU, HPC, STB, SSD controllers, and application processors.

View GDDR6 PHY IP for 12nm full description to...

- see the entire GDDR6 PHY IP for 12nm datasheet

- get in contact with GDDR6 PHY IP for 12nm Supplier

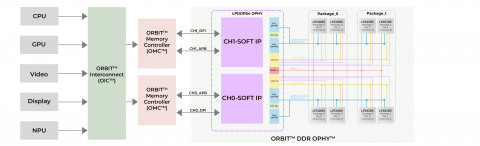

Block Diagram of the GDDR6 PHY IP for 12nm IP Core