Hardware RTP Stack for H.264 Stream Decapsulation

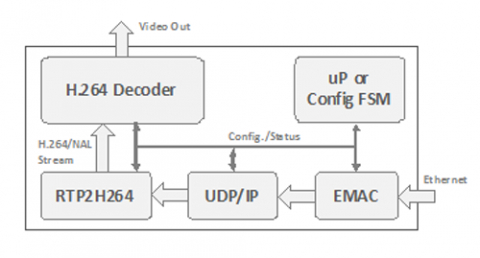

The RTP2Η264 core is compatible with RTP packets produced by CAST’s H.264 to RTP encapsulation core (H2642RTP). The output of the RTP2Η264 can be directly connected to the input of an H.264 decoder core. Along with CAST’s UDP/IP hardware stack, the RTP2Η264 core is ideal for offloading the demanding task of RTP/UDP/IP de-capsulation from a host processor, and enables H.264 video streaming even in processor-less SoC designs.

The core is easy to integrate in systems with or without a host processor. H.264 stream and RTP packet data can are input/output via dedicated streaming-capable interfaces, enabling direct connection to hardware video encoders and hardware stacks for UDP or TCP. Status and control registers are accessible by an AXI4-Lite interface.

The RTP2Η264 core is available in RTL source or as a targeted FPGA netlist. Platforms integrating the core along H.264 decoder, UDP/IP, and eMAC cores, are also available from CAST, and can enable rapid development of video over IP systems.

View Hardware RTP Stack for H.264 Stream Decapsulation full description to...

- see the entire Hardware RTP Stack for H.264 Stream Decapsulation datasheet

- get in contact with Hardware RTP Stack for H.264 Stream Decapsulation Supplier

Block Diagram of the Hardware RTP Stack for H.264 Stream Decapsulation

Hardware RTP Stack IP

- RTP / UDP / IP Hardware Stack for Raw, Uncompressed RGB/YUV Video Streams

- RTP / UDP / IP Hardware Stack for H.264/H.265 NAL Video Streams Packet Processing

- Hardware RTP Stack for H.264 Stream Encapsulation

- Hardware RTP Stack for JPEG Stream Encapsulation

- Hardware RTP Stack for H.264 Stream Decapsulation

- RTP Transmitter