High Performance, Low Latency PCIe Gen5 PHY

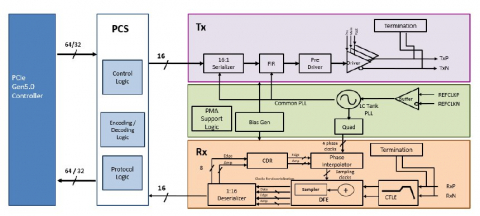

The PMA ( Physical Media Attachment) is delivered as hard macro and the PCS ( Physical Coding sublayer ) as a synthesizable soft macro. The integrated PHY ( PCS+PMA) of PCIe Gen 5 is backward compatible to PCIe Gen 4/3/2/1/ and designed for various applications like chip_to_chip communication, SSD, HPC for enterprise solutions supporting upto 36dB channel loss. Our PHY architecture support wide range of links with our unique CMU (Clock Management Unit).

PHY IP provides high-performance low power architecture having multi-lane capability for the high-bandwidth applications. It meets the needs of today’s high speed chip-to-chip, board-to-board, and backplane interfaces while being low in power and area.

View High Performance, Low Latency PCIe Gen5 PHY full description to...

- see the entire High Performance, Low Latency PCIe Gen5 PHY datasheet

- get in contact with High Performance, Low Latency PCIe Gen5 PHY Supplier

Block Diagram of the High Performance, Low Latency PCIe Gen5 PHY

PCIe 5.0 PHY IP

- PCIe 5.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- PCIe 5.0 PHY in TSMC (16nm, 12nm, N7, N6, N5, N4P, N3E, N3P)

- PCIe 5.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

- PCIe 5.0 Controller with AMBA AXI interface

- PCIe 5.0 Customizable Embedded Multi-port Switch

- PCIe 5.0 PHY IP for Storage and High-Bandwidth Connection