Software Defined Radio with Spread spectrum and SOQPSK for Telemetry applications

Extended MIPI CSI2 Receiver IP Core

This development requires high bandwidth between the camera and the application processor.

For example, a commercially available 4068x3456 30 fps camera outputs an average of over 5Gbps,

which requires 4 DPHY lanes at more than 1.25Gbp – more the original 1Gpbs of MIPI DPHY 1.0,

but still manageable by the extended 1.5Gbps of the latest DPHY spec.

However, when the same or similar camera is introduced with 60fps, over 10Gbps will be required,

and 4 lanes will not suffice.

MIPI’s forthcoming new set of standards (CSI3 over UNIPRO and MPHY) will offer higher bandwidth.

However, until those standards are available, camera vendors are looking for ways to increase CSI2 speed.

Among others, extension of the CSI2 standard to 8 data lanes, with one or two clock lanes, are introduced.

Application processor vendors also face speed issues. Processing frames of 16 million pixel at 60 fps

require the processing of 1G pixel per second. As employing a 1GHz clock is not desirable, the trend is to

process more than one pixel in each clock cycle.

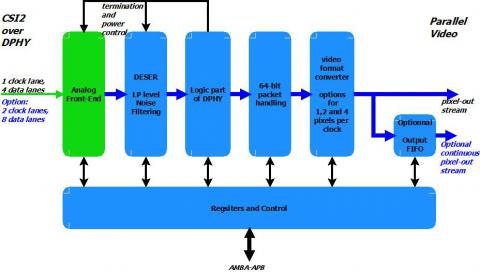

VLSI Plus' SVRPlus-CSI2-I IP core is designed to support those trends, and, at the same time, work with a

relatively slow clock rate, processing several pixels per clock.

The SVRPlus-CSI2-I has an internal 64-bit bus. With this bus width, 10Gbps can be handled by a reasonable 167MHz clock.

The output path of the SVRPlus-CSI2-I can handle 1, 2 or 4 pixels in parallel. Image sensors which generate, for example,

12M * 60 fps = 720M pixels per second, can be handled by the SVRPlus-CSI2-I driven by a 180MHz clock, if the

PARALLEL_PIXELS compilation switch is set to 4.

The SVRPlus-CSI2-I can handle up to 8 data lanes, with one or two clock lanes, and at up to 1.5Gbps per lane.

If extended CSI2 is not required, the customer can save gate count and off-FPGA circuits by setting the EIGHT_LANES

compilation switch to NO.

View High Performance Second Generation Extended MIPI CSI2 Receiver full description to...

- see the entire High Performance Second Generation Extended MIPI CSI2 Receiver datasheet

- get in contact with High Performance Second Generation Extended MIPI CSI2 Receiver Supplier

Block Diagram of the Extended MIPI CSI2 Receiver IP Core

MIPI CSI2 Receiver IP

- MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- Very compact (500 LUTs) Camera Sensor Receiver Interface Converting from MIPI CSI-2 to AXI4-Stream Video Standard

- MIPI D-PHY CSI-2 RX (Receiver) in Samsung 28FDSOI

- MIPI D-PHY CSI-2 RX+ (Receiver) IP in TSMC 28HPM

- 2.5Gbps Per Lane MIPI-CSI2 Compliant Serial Video Receiver

- MIPI D-PHY CSI-2 RX+ (Receiver) IP in TSMC 40LP