High Resolution Low Latency Sigma-Delta ADC

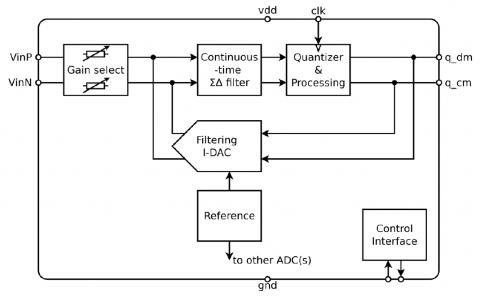

The latency of the ADC is only one clock cycle (40ns at 25MHz), which makes the converter ideally suited for application in control loops. The low latency is enabled by feeding the bitstream output back to the input via a DAC with build-in filtering. This creates a “tracking ADC behavior”, where the output accurately tracks the input signal inside the signal bandwidth. Next to enabling low latency, the filtering DAC also makes the system robust towards jitter and other error sources typically associated with 1-bit converters.

The Low Latency Sigma-Delta ADC can convert both single-ended and differential signals with high accuracy. Next to this it can convert signals with amplitudes and biasing levels well outside its own supply level, by using external resistors acting as level shifters.

View High Resolution Low Latency Sigma-Delta ADC full description to...

- see the entire High Resolution Low Latency Sigma-Delta ADC datasheet

- get in contact with High Resolution Low Latency Sigma-Delta ADC Supplier

Block Diagram of the High Resolution Low Latency Sigma-Delta ADC

Sigma Delta ADC IP

- 16 Bit 10 kS/s Incremental Delta - Sigma ADC

- 32 bit 8Ksps sigma delta ADC for Seismic Precision application in TSMC 180nm

- 16-bit Sigma Delta ADC

- Extended Range Incremental Sigma Delta ADC

- 250MHz, 12-bit High Speed Delta Sigma ADC for 5G, LiDAR and Imaging

- 400MHz, 12-bit High Speed Delta Sigma ADC for 5G, LiDAR and Imaging