High speed NoC (Network On-Chip) Interconnect IP

Today’s SoC gets increasingly complex and performance-demanding with multi-core & multiple DRAM channels. Conventional crossbar-based bus design fails to meet these requirements, significantly increasing overall SoC design efforts. OIC is the next-generation high-speed interconnect IP, which features high performance, small area & ultra-low power consumption through proprietary HyperPath technology and proprietary Asynchronous Bridge technology. With these proven & unique technologies, OIC enables customers to reduce SoC’s backbone area (& global wires) by almost half while satisfying SoC’s high bandwidth and low latency demand. OIC’s automated end-to-end interconnect generation flow provides SoC design flexibility, significantly reducing SoC design efforts.

View High speed NoC (Network On-Chip) Interconnect IP full description to...

- see the entire High speed NoC (Network On-Chip) Interconnect IP datasheet

- get in contact with High speed NoC (Network On-Chip) Interconnect IP Supplier

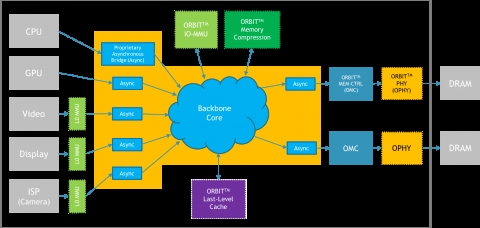

Block Diagram of the High speed NoC (Network On-Chip) Interconnect IP