NVM OTP in UMC (180nm, 153nm, 110nm, 90nm, 80nm, 55nm, 40nm, 28nm, 22nm)

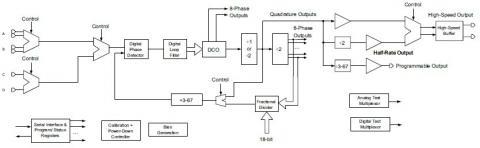

High-Speed, Wide-Range Digital PLL in TSMC 40LP

View High-Speed, Wide-Range Digital PLL in TSMC 40LP full description to...

- see the entire High-Speed, Wide-Range Digital PLL in TSMC 40LP datasheet

- get in contact with High-Speed, Wide-Range Digital PLL in TSMC 40LP Supplier

Block Diagram of the High-Speed, Wide-Range Digital PLL in TSMC 40LP

PLL in TSMC 40nm IP

- TSMC GF Intel Samsung Deskew Frequency Synthesizer PLL

- TSMC GF Intel Samsung Fractional-N Frequency Synthesizer PLL

- TSMC GF Intel Samsung Integer-N Frequency Synthesizer PLL

- TSMC Intel 32kHz Low-bandwidth Frequency Synthesizer PLL

- MIPI D-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)