HMAC-SHA-2 (224/256/384/512) 100 Million Trace DPA Resistant Crypto Accelerato

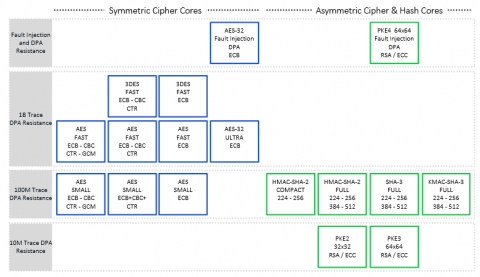

The DPA Resistant Hardware cores offer chipmakers an easy-to-integrate technology-independent soft-macro security solution with built-in side-channel resistance for cryptographic functions across a wide array of devices.

These high-performance cores provide a higher level of protection than standard security cores, while improving time-to-market, as all the cores are validated DPA countermeasures. It is highly flexible for integration with standard cipher modes such as Cipher Block Chaining (CBC), Counter (CTR) and Authenticated Encryption mode / Galois Counter (GCM) modes. The fast AES core performs AES encryption with DPA protection using only 2 clock cycles per AES round, outperforming any existing solution.

View HMAC-SHA-2 (224/256/384/512) 100 Million Trace DPA Resistant Crypto Accelerato full description to...

- see the entire HMAC-SHA-2 (224/256/384/512) 100 Million Trace DPA Resistant Crypto Accelerato datasheet

- get in contact with HMAC-SHA-2 (224/256/384/512) 100 Million Trace DPA Resistant Crypto Accelerato Supplier

Block Diagram of the HMAC-SHA-2 (224/256/384/512) 100 Million Trace DPA Resistant Crypto Accelerato

Rambus Cryptographic Accelerator Core HMAC-SHA-2 IP

- AES-ECB-CBC-CFB-CTR-GCM 1 Billion Trace DPA & Fault Injection Resistant Crypto Accelerator

- Whirlpool Crypto Accelerator

- AES-ECB 1 Billion Trace DPA & Fault Injection Resistant Crypto Accelerator

- ChaCha20 DPA Resistant Crypto Accelerator

- RSA-ECC Public Key Accelerator Engine, 750K ops/sec

- RSA-ECC Public Key Accelerator Engine, 50K ops/sec