Hs-Mode I2C Controller - 3.4 Mbps, Master w/FIFO

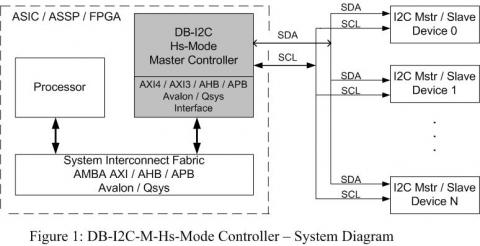

The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master / slave controller and one or more master / slave devices.

View Hs-Mode I2C Controller - 3.4 Mbps, Master w/FIFO full description to...

- see the entire Hs-Mode I2C Controller - 3.4 Mbps, Master w/FIFO datasheet

- get in contact with Hs-Mode I2C Controller - 3.4 Mbps, Master w/FIFO Supplier

Block Diagram of the Hs-Mode I2C Controller - 3.4 Mbps, Master w/FIFO