IEEE 802.1 Clause 4 MAC

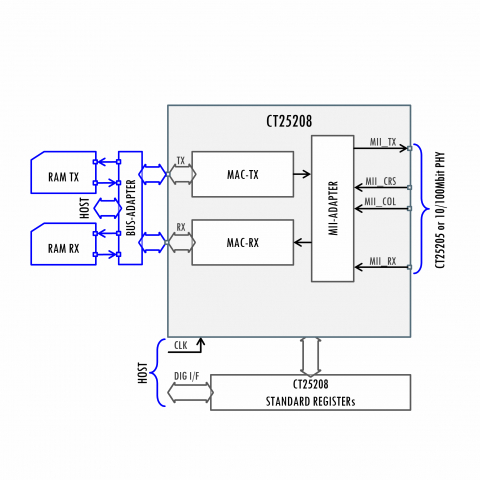

On the other end, the CT25208 features a proprietary, MII-like Reconciliation Sublayer (RS) interface, including adapter modules to interface with standard MII/RMII PHYs.

The RTL code is written in plain Verilog 2005 HDL, and it is fully synthesizable on standard cells and FPGA systems.

The flexible MAC Client interface can also be configured for transferring 1, 2, or 4 bytes at a time, supporting both little-endian and big-endian byte order. This feature allows the CT25208 IP to be used with many MCUs and other systems based on shared-memory access by means of a dedicated Bus Adapted interface.

The CT25208 can be used in conjunction to others analog and digital blocks like (a) the CT25205 to implement a digital 10BASE-T1S MACPHY and (b) the CT25203, the CT25205 and the CT25209 to implement a complete OPEN Alliance MACPHY.

View IEEE 802.1 Clause 4 MAC full description to...

- see the entire IEEE 802.1 Clause 4 MAC datasheet

- get in contact with IEEE 802.1 Clause 4 MAC Supplier

Block Diagram of the IEEE 802.1 Clause 4 MAC IP Core

IEEE 802.1 Clause 4 MAC IP

- 1.6T Ethernet PCS IP based on the IEEE 802.3dj spec for 400Gbps, 800Gbps & 1.6Tbps Ethernet applications

- Clause 74 FEC

- 40G/100G Ethernet PCS/MAC IP Cores

- IEEE 802.3cg® 10BASE-T1S Digital Controller

- Ethernet PCS 100G

- Triple-speed (10Mbps/100Mbps/1Gbps) Ethernet Layer-2 switch that supports new protocols, providing seamless redundancy for Ethernet networking