DDR5/DDR4/LPDDR5 Combo PHY IP - 4800Mbps (Silicon Proven in TSMC 12FFC)

IEEE1588 & IEEE802.1AS PTP Hybrid Clock (HC) core

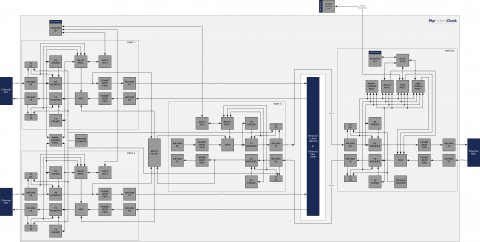

The HC is intercepting the path between an Ethernet PHY and an Ethernet core that forwards or handles Ethernet frames. Mostly this is used in daisy-chained networks. This allows message injection in parallel to data transfers from/to the Switching Core.

All datasets and algorithms are implemented completely in HW.

View IEEE1588 & IEEE802.1AS PTP Hybrid Clock (HC) core full description to...

- see the entire IEEE1588 & IEEE802.1AS PTP Hybrid Clock (HC) core datasheet

- get in contact with IEEE1588 & IEEE802.1AS PTP Hybrid Clock (HC) core Supplier

Block Diagram of the IEEE1588 & IEEE802.1AS PTP Hybrid Clock (HC) core

PTP IP

- Software Defined Radio for High Throughput PTP and PTMP network communication

- 10 Gigabit Ethernet MAC with IEEE 1588 PTP Support and AVB for Auto

- IEEE1588 & IEEE802.1AS PTP Ordinary Clock (OC) core

- IEEE1588 & IEEE802.1AS PTP Transparent Clock (TC) core

- IEEE1588 & IEEE802.1AS PTP Timestamp Unit (TSU) core

- Gigabit Ethernet MAC with IEEE 1588 PTP Support and AVB for Auto