Interlaken Controller

The Interlaken Controller can be widely used in chip-to-chip transfers, it has an extensive feature-set available and allows scalability in number of logic channels (up to 2048), lanes (up to 48) and lane speed (up to 56 Gbps). The IP core is heavily tested in SystemVerilog random regression environment.

View Interlaken Controller full description to...

- see the entire Interlaken Controller datasheet

- get in contact with Interlaken Controller Supplier

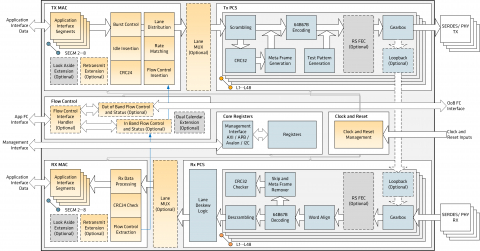

Block Diagram of the Interlaken Controller IP Core

Interlaken IP

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- Multi-protocol SerDes PMA in FDSOI (GF22FDX FDX 22FDX) - PCIe1 PCIe2 PCIe3 PCIe4 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- Interlaken Controller

- Interlaken Communication Controller

- Interlaken, 100G, 12 Lanes