AMBA Parameter Configurable Multi-Channel DMA Controller (typically 1 to 256)

LIN Bus Master/Slave Controller Core

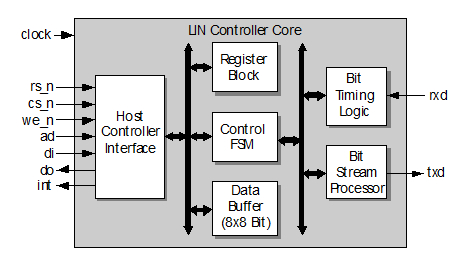

The LIN controller can be implemented as a master or as a slave and operate on LIN 1.3, 2.0, 2.1 or 2.2 LIN network. It uses a single master/multiple slave concept for message transfer between nodes of the LIN network. The message transfer can be controlled via a microcontroller interface and a LIN transceiver is needed for the connection to the LIN bus.

The LIN-CTRL is used to interface sensors and actuators in a variety of applications such as automotive, industrial, and home appliances.

The core is a microcode-free design developed for reuse in ASIC and FPGA implementations. The scan-ready design is strictly synchronous with positive-edge clocking and no internal tri-states. The robustly verified core has been production-proven multiple times.

The LIN-CTRL core is available in two versions: Standard, and Safety-Enhanced. The Safety-Enhanced version implements ECC for SRAMs protection and uses spatial redundancy for protecting the inner logic of the core. The Safety-Enhanced versions are certified as ISO-26262 ASIL-D Ready. More ISO-26262

View LIN Bus Master/Slave Controller Core full description to...

- see the entire LIN Bus Master/Slave Controller Core datasheet

- get in contact with LIN Bus Master/Slave Controller Core Supplier

Block Diagram of the LIN Bus Master/Slave Controller Core