Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference

View Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference full description to...

- see the entire Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference datasheet

- get in contact with Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference Supplier

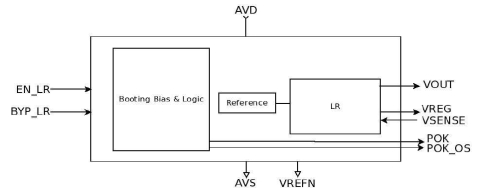

Block Diagram of the Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference