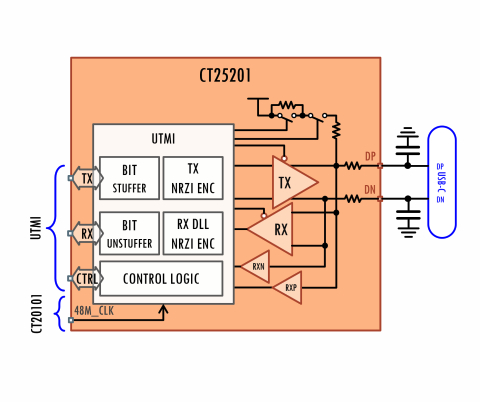

Low/Full Speed USB Physical Layer

To minimize the number of external components, the CT25201 integrates the DN/DP termination resistors and the pull-up resistor on DN.

A standard UTMI digital interface which perform low level packet encoding, decoding, serialization, deserialization including bit-stuffing permits an easy interface with the most diffused USB controllers.

View Low/Full Speed USB Physical Layer full description to...

- see the entire Low/Full Speed USB Physical Layer datasheet

- get in contact with Low/Full Speed USB Physical Layer Supplier

Block Diagram of the Low/Full Speed USB Physical Layer

USB PHY IP

- USB 2.0 PHY TSMC 5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm, 65nm, 130nm, 180nm

- USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- USB 2.0 OTG High / Full / Low- Speed Dual Role IP Core

- USB 3.1 PHY (10G/5G) inTSMC (16nm, 12nm, N7, N6, N5,N3E, N3P)

- USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in TSMC 22ULP