Low-Latency 10/100/1000 Ethernet MAC

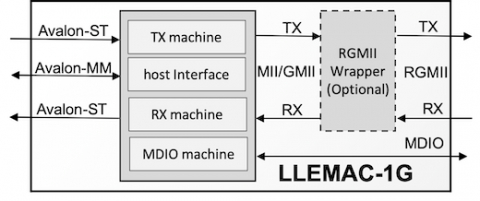

The core supports full-duplex operation, supports jumbo frames, provides statistics counters, and it is easy to integrate and implement. The LLEMAC-1G exchanges data with the host system via a byte-wide streaming interfaces, and connects to the external PHY via an MII, GMII or RGMII interfaces. An independently clocked, 32-bit wide memory mapped interface provides access to the cores control and status registers. The default core interfaces comply to the Avalon standard, but AMBA™ AHB or AXI can also be made available upon request.

View Low-Latency 10/100/1000 Ethernet MAC full description to...

- see the entire Low-Latency 10/100/1000 Ethernet MAC datasheet

- get in contact with Low-Latency 10/100/1000 Ethernet MAC Supplier

Block Diagram of the Low-Latency 10/100/1000 Ethernet MAC IP Core