Multi-Protocol Engine with Classifier, Look-Aside, 5-10 Gbps

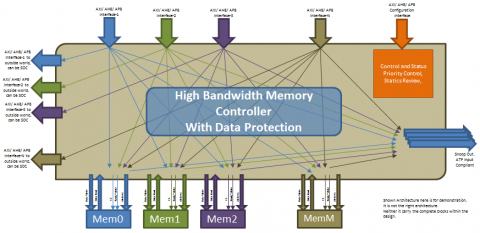

Low Latency Interconnect for AI/ML (GreenIPCore Shared Multi Memory Integration Controller (SMMIC))

GreenIPCore Low Latency Interconnect for AI/ML Shared Multi Memory Integration Controller is a memory controller with option to have multiple masters connected to access a memory. And on the memory side, it enables user to connect more than one memory clubbed together to make a bigger memory. In this way smaller memory segment are created to enable users to make much bigger memory system. This system has much higher data rate and same memory can be accessed by multiple masters.

View Low Latency Interconnect for AI/ML (GreenIPCore Shared Multi Memory Integration Controller (SMMIC)) full description to...

- see the entire Low Latency Interconnect for AI/ML (GreenIPCore Shared Multi Memory Integration Controller (SMMIC)) datasheet

- get in contact with Low Latency Interconnect for AI/ML (GreenIPCore Shared Multi Memory Integration Controller (SMMIC)) Supplier

Block Diagram of the Low Latency Interconnect for AI/ML (GreenIPCore Shared Multi Memory Integration Controller (SMMIC))

Multiple Memories IP

- Silicon-proven, High Density and Low Power Static Random Access Memories

- FlexRay Controller

- x2 - 8-bit RISC Microcontroller

- Complete memory system supporting any combinations of SDR SDRAM, DDR, DDR2, Mobile SDR, FCRAM, Flash, EEPROM, SRAM and NAND Flash, all in one IP core

- low power, high speed, and high density configurable CAM

- SDRAM Multi-client Controller (two read clients and two write clients)*