Fractional-N Integer LC DESKEW PLLs in FDSOI FDX (GF22FDX SS28FDS ST28FD-SOI 22FDX 28FDS)

Low-leakage LDO in TSMC 22ULL supporting up to 3.63 V input voltage

View Low-leakage LDO in TSMC 22ULL supporting up to 3.63 V input voltage full description to...

- see the entire Low-leakage LDO in TSMC 22ULL supporting up to 3.63 V input voltage datasheet

- get in contact with Low-leakage LDO in TSMC 22ULL supporting up to 3.63 V input voltage Supplier

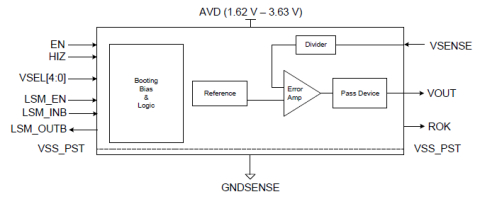

Block Diagram of the Low-leakage LDO in TSMC 22ULL supporting up to 3.63 V input voltage