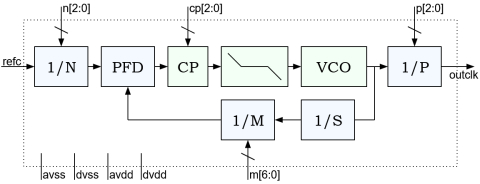

Low Power PLL for 55nm UMC ULP CMOS

View Low Power PLL for 55nm UMC ULP CMOS full description to...

- see the entire Low Power PLL for 55nm UMC ULP CMOS datasheet

- get in contact with Low Power PLL for 55nm UMC ULP CMOS Supplier

Block Diagram of the Low Power PLL for 55nm UMC ULP CMOS

clock IP

- TSMC CLN7FF 7nm Clock Generator PLL - 800MHz-4000MHz

- TSMC Samsung GF Intel CML mux - on-chip clock buffer

- TSMC FPD-Link / OpenLDI / LVDS forwarded clock SERDES Link

- Adaptive Clock Generation Module for DVFS and Droop Response

- TSMC 12 FFC 4GHz & 8GHz Clock Generator / Clock Synthesizer, PLL (Fractional / Integer)

- TSMC CLN20SOC 20nm Clock Generator PLL - 700MHz-3500MHz