LPDDR5X/5/4X/4 combo PHY at Samsung SF5A

The LPDDR5X/5/4X/4 Combo OPHY features a state-of-art mixed-signal architecture that addresses the challenges of DRAM integration in high-performance and low-power environments. This architecture enables LPDDR5/4 Combo OPHY to overcome issues with long-term impedance drift and clock phase drift, allowing impedance and clock phase updates without interruption of data traffic. The programmable timing at the OPHY boundary combines flexibility with analog precision, resulting in low read/write latency between OMC and the LPDDR5X/5/4X/4 DRAM without sacrificing performance.

The LPDDR5X/5/4X/4 Combo OPHY was designed with subsystem and system-level considerations in mind. Built-in power management logic and advanced PLL design allow aggressive power state management and optimal system power usage.

At the system level, the LPDDR54 Combo OPHY was designed to minimize package substrate layer and PCB layer requirements, enabling usage in cost-sensitive applications and application processors.

View LPDDR5X/5/4X/4 combo PHY at Samsung SF5A full description to...

- see the entire LPDDR5X/5/4X/4 combo PHY at Samsung SF5A datasheet

- get in contact with LPDDR5X/5/4X/4 combo PHY at Samsung SF5A Supplier

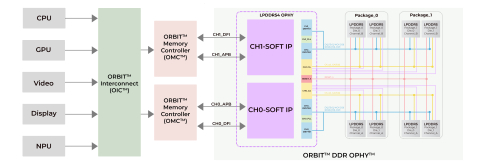

Block Diagram of the LPDDR5X/5/4X/4 combo PHY at Samsung SF5A