55nmHV MTP Non Volatile Memory for Standard CMOS Logic Process

LZ4/Snappy Data Decompressor

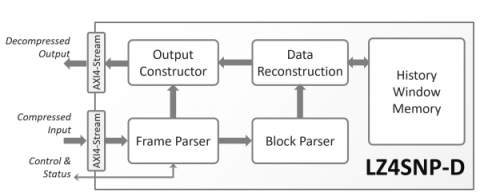

The core features fast processing with low latency and high throughput. In its default configuration, LZ4SNP-D outputs 7.8 bytes of decompressed data per clock cycle and can be clocked at frequencies exceeding 1 GHz in modern ASIC technologies. Designers can scale the throughput by instantiating the core multiple times to achieve throughput rates exceeding 100Gbps. The processing latency is approximately 30 clock cycles.

The decompression core operates on a standalone basis—offloading the host CPU from the demanding task of data decompression—and has been designed for easy integration and use. No preprocessing of the incoming compressed files is required, as the core parses the file headers, checks the input files for errors, and outputs the decompressed data payload.

Extensive error tracking and reporting enable the core to ensure smooth system operation and error recovery, even in the presence of errors in the compressed input files. Furthermore, internal memories can optionally support Error Correction Codes (ECC) to simplify achieving enterprise-class reliability or functional safety requirements.

The LZ4SNP-D core is a microcode-free design developed for reuse in ASIC and FPGA implementations. Its streaming data interface—optionally bridged to AMBA® AXI4-Stream—eases SoC integration. Technology mapping is straightforward, as the design is scan-ready, LINT-clean, microcode-free, and uses easily replaceable, generic memory models.

View LZ4/Snappy Data Decompressor full description to...

- see the entire LZ4/Snappy Data Decompressor datasheet

- get in contact with LZ4/Snappy Data Decompressor Supplier

Block Diagram of the LZ4/Snappy Data Decompressor IP Core