- Silicon IP Catalog >

- Wireline Communication >

- Modulation/Demodulation >

- Quadrature Amplitude Modulation

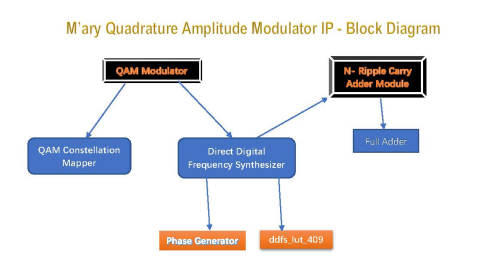

M’ary Quadrature Amplitude Modulator IP in VHDL, FPGA and SDR

The modulator is targeted at the low-level "RTL based" implementation with the building blocks of the QAM modulator. To provide a flexible way of testing the transmission and modulation properties later in real-time, a higher level hierarchical implementation based on GNURadio was provided to investigate future application of offloading QAM modulation into FPGA, to accelerate the development, testing, and verification of SDR (Software-Defined Radio) application in real-time environment.

View M’ary Quadrature Amplitude Modulator IP in VHDL, FPGA and SDR full description to...

- see the entire M’ary Quadrature Amplitude Modulator IP in VHDL, FPGA and SDR datasheet

- get in contact with M’ary Quadrature Amplitude Modulator IP in VHDL, FPGA and SDR Supplier

Block Diagram of the M’ary Quadrature Amplitude Modulator IP in VHDL, FPGA and SDR