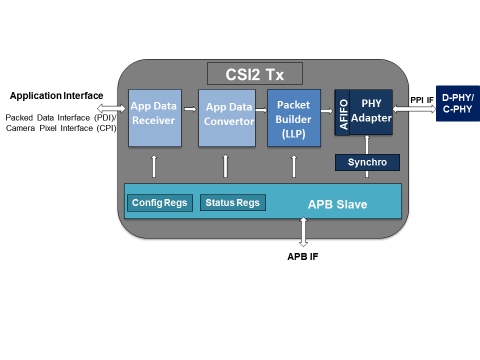

MIPI CSI2 v1.3 Transmit Controller

CSI2 Tx v1.3 Transmitter supports two High-Speed serial interface options, D-PHY and C-PHY option. Depending on the chosen serial interface option, C-PHY 1.0 or D-PHY 1.2 is the physical layer block to which the MIPI CSI-2 Transmit controller interfaces for transmission.

CSI2 Tx converts received data into byte stream that follows the generic CSI2 protocol mapping rule. This IP calculates and appends an ECC or CRC value to packet header depending on the choice of the physical layer. For the payload of a long packet CSI2 Tx calculates its CRC value and appends to the packet as a footer and inserts packet Filler bytes after the Packet Footer, if needed. The packet is buffered in a FIFO and synchronized to the High-Speed Transmit clock domain and distributed to one or more data lanes depending on the lane distribution scheme set by the camera sensor. Packets are sent over D-PHY’s or C-PHY’s PPI interface depending on the PHY technology (D-PHY or C-PHY).

View MIPI CSI2 v1.3 Transmit Controller full description to...

- see the entire MIPI CSI2 v1.3 Transmit Controller datasheet

- get in contact with MIPI CSI2 v1.3 Transmit Controller Supplier

Block Diagram of the MIPI CSI2 v1.3 Transmit Controller IP Core

MIPI CSI-2 Controller IP

- MIPI CSI-2 Controller Core V2

- MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI CSI-2 RX Controller for v2.1

- MIPI CSI-2 TX Controller for v2.1

- MIPI CSI2 Transmit Controller