MIPI D-PHY TSMC 40LP

The D-PHY provides a point to point connection between master and slave or host and device that comply with a relevant MIPI® standard. A typical configuration consists of a clock lane and 1-4 data lanes. The master/host is primarily the source of data and the slave/device is usually the sink of data. The D-PHY lanes can be configured for unidirectional or bidirectional lane operation, originating at the master and terminating at the slave. It can be configured to operate as a master or as a slave. The D-PHY link supports a high speed (HS) mode for fast data traffic and a low power (LP) mode for control transactions. In HS mode, the low swing differential signal is able to support data transfers from 80 Mbps to 1.5 Gbps. In LP mode all wires operate as a single ended line capable of supporting 10 Mbps asynchronous data communications.

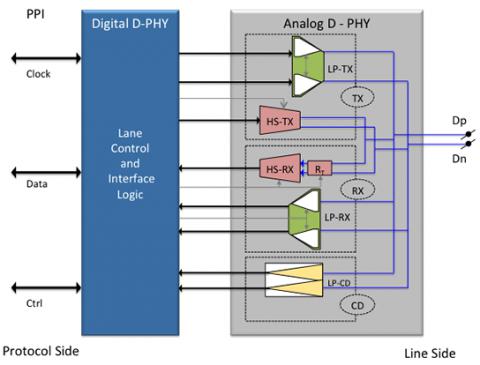

The D-PHY Analog Transceiver IP core implements the PPI interface recommended by the MIPI® working groups to easily interface to the required protocols.

View MIPI D-PHY TSMC 40LP full description to...

- see the entire MIPI D-PHY TSMC 40LP datasheet

- get in contact with MIPI D-PHY TSMC 40LP Supplier

Block Diagram of the MIPI D-PHY TSMC 40LP IP Core