Ceva-Waves Bluetooth 5.3 Low Energy Baseband Controller, software and profiles

MIPI DSI-2 Transmit Controller v1.0

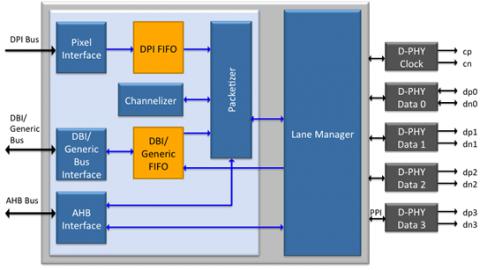

On the application processor side, Arasan’s DSI Host Controller provides the choice of DPI or DBI Interface to a graphics controller. A DBI interface provides downstream support of Types 1 to 3 display modules, and the DPI Interface is needed for Types 2 to 4 displays.

Initial configuration of this IP can be done through programmed IO over the AHB bus, however, other bus interfaces can be provided upon request.

View MIPI DSI-2 Transmit Controller v1.0 full description to...

- see the entire MIPI DSI-2 Transmit Controller v1.0 datasheet

- get in contact with MIPI DSI-2 Transmit Controller v1.0 Supplier

Block Diagram of the MIPI DSI-2 Transmit Controller v1.0 IP Core

DSI IP

- MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI DSI Receiver Controller v1.3

- MIPI DSI Transmit Controller v1.3

- MIPI D-PHY / C-PHY Combo IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI D-PHY Universal IP in TSMC 22ULP

- MIPI C-PHY/D-PHY Combo TX+ IP 4.5Gsps/4.5Gbps in TSMC N5