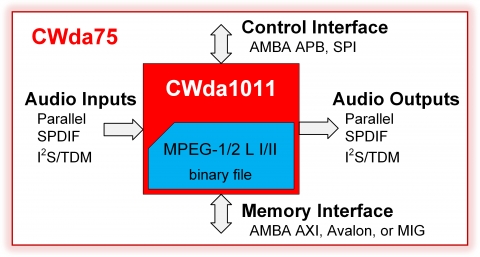

MPEG-1/2 – Layer I/II Audio Decoder

This core contains the MPEG-1/2 – Layer I/II decoder software and the Coreworks processor based hardware audio engine platform (CWda1011).

The software is compiled into an image file (.bin) which can be automatically boot-loaded through one of the control interfaces (parallel AMBA APB or serial SPI) and run on the audio engine platform with simple parameters setting.

The program can be configured, controlled and monitored by means of a configuration, control, and status register file, accessed by the control interfaces.

The audio input and output interfaces uses a native parallel interface. Other standard audio interfaces, such as I2S/TDM and SPDIF are also available.

The interface to the external memory can be one of the following: AMBA AXI (for ASICs or Xilinx FPGAs), Avalon (for Altera FPGAs) or MIG (for Xilinx FPGAs).

The CWda1011 platform is an instance of the generic CWdaXYZ audio engine platform. Other platforms are available for a different number of audio channels (from 2 channels, up to 32 channels). Please contact us to select the best solution for your requirements.

View MPEG-1/2 – Layer I/II Audio Decoder full description to...

- see the entire MPEG-1/2 – Layer I/II Audio Decoder datasheet

- get in contact with MPEG-1/2 – Layer I/II Audio Decoder Supplier

Block Diagram of the MPEG-1/2 – Layer I/II Audio Decoder

Digital audio IP

- Digital audio PDM-to-PCM converter with 117 dB Dynamic Range and Dual-phase alignment

- I2S/Left-Justified/TDM Digital Audio Interface

- 16-22Bit 97dB Stereo Audio CODEC with Linein/Digital and Analog Microphone Recording, Lineout/Headphone/Speaker Playback, SMIC 65nmll

- 24-bit pure digital audio CODEC with 100 dB SNR stereo PDM-to-PCM and up to 110 dB SNR stereo PWM DAC with ASRC

- 100 dB of SNR, 24-bit stereo audio CODEC with headphone driver and digital mixer

- Dolby Digital/AC-3/MPEG Audio Decoding Core