55nmHV MTP Non Volatile Memory for Standard CMOS Logic Process

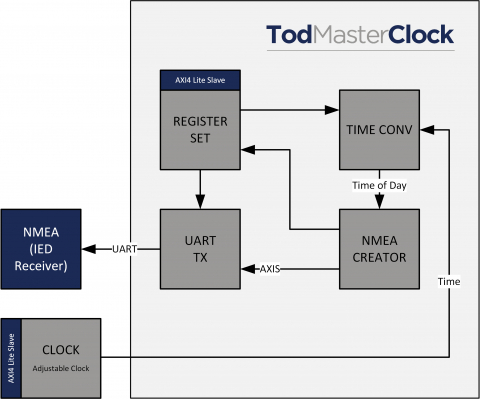

NMEA Time of Day (ToD) Master core

All calculations and corrections are implemented completely in HW.

View NMEA Time of Day (ToD) Master core full description to...

- see the entire NMEA Time of Day (ToD) Master core datasheet

- get in contact with NMEA Time of Day (ToD) Master core Supplier

Block Diagram of the NMEA Time of Day (ToD) Master core