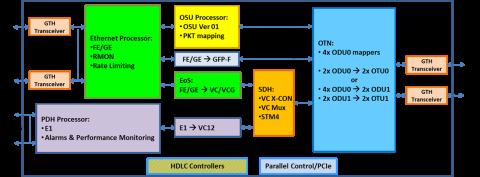

The TPS3215MP OSU processor is an IP Core solution designed for Xilinx FPGAs. TPS3215MP processors accept 4x FE/GE and 4x E1 client signals, process and present them to either SDH VC, OSU or ODU containers for their transport over OTU0/OTU1 bearers. TPS3215MP processors include an Ethernet-over-SDH (EoS) capability. The OTU line signals can be configured in 1+1 protection configurations, offering protection at the OTU/ODU/OSU/SDH levels. For Ethernet client-services, Ethernet rate-limiting is provided. TPS3215MP processors support hitless bandwidth adjustment of OSU containers carrying Ethernet information. Integrated HDLC controllers can be assigned to GCC in-band communications channels. TPS3215MP processors are offered as complete turn-key solutions for Xilinx FPGAs, including built-in jitter attenuators.