PCI Express 4.0 PHY

The PCIe IP boasts a low power consumption and compact silicon footprint. Its robust PHY architecture tolerates process, voltage, and temperature (PVT) variations. This IP integrates high-speed mixed-signal circuits to support PCIe 4.0 traffic at 16Gbps. It is backward compatible with PCIe 3.1 data rates at 8.0Gbps, PCIe 2.1 at 5.0Gbps, and PCIe 1.1 at 2.5Gbps. The multi-tab transceiver design, accompanied by a robust BIST, an embedded bit error rate (BER) tester, and an internal eye monitor, enables designers to control, test, and monitor signal integrity without the need for expensive test equipment.

View PCI Express 4.0 PHY full description to...

- see the entire PCI Express 4.0 PHY datasheet

- get in contact with PCI Express 4.0 PHY Supplier

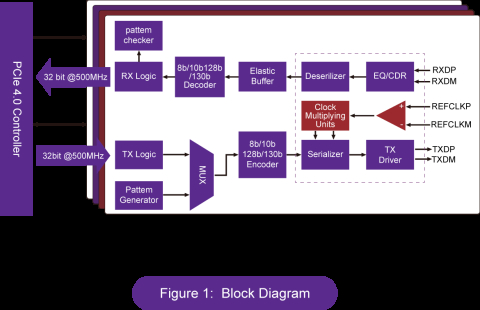

Block Diagram of the PCI Express 4.0 PHY IP Core

PCI express PHY IP

- PCIe 7.0 PHY IP supporting the latest features of the evolving PCIe 7.0 specification to enable 128 GT/s and up to x16 lane configurations

- PCIe 5.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- PCI Express PHY serial link PIPE Transceiver IP cell/hard macro

- PCI Express GEN-3/Display Port SERDES PHY - Samsung 28 28LPP

- PCI Express GEN-3/SATA3 SERDES PHY - Samsung 28 28FDSOI

- PCI Express GEN 3/4 Port SERDES PHY - Samsung 14LPP