PCIe 2.0 Serdes PHY IP, Silicon Proven in TSMC 28HPCP

The PCIe2.0 PHY IP transceiver is optimized for low power consumption and minimal die area, without sacrificing performance and high-data throughput. The PCIe2.0 PHY IP comprises a complete on-chip physical transceiver solution with Electrostatic Discharge (ESD) protection, built-in self-test module with embedded jitter injection, and a dynamic equalization circuit that ensures full support for highperformance designs.

View PCIe 2.0 Serdes PHY IP, Silicon Proven in TSMC 28HPCP full description to...

- see the entire PCIe 2.0 Serdes PHY IP, Silicon Proven in TSMC 28HPCP datasheet

- get in contact with PCIe 2.0 Serdes PHY IP, Silicon Proven in TSMC 28HPCP Supplier

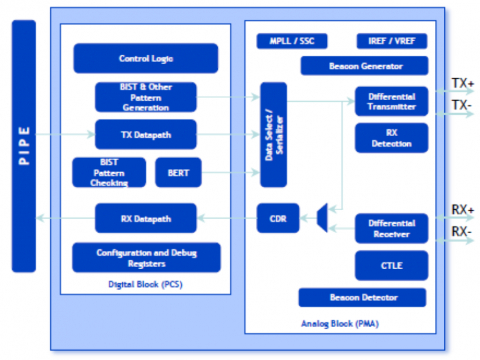

Block Diagram of the PCIe 2.0 Serdes PHY IP, Silicon Proven in TSMC 28HPCP