PCIe Gen1/2 PHY

MAC

PCS

PIPE interface (8 bit, 16 bit and 32 bit interface)

Scrambler

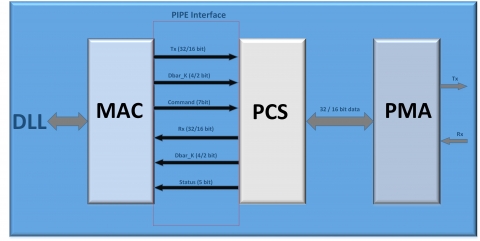

The PHY layer is essentially the PIPE (Physical Interface for PCIe Express). The designed PIPE interface follows the INTEL’s PIPE spec. This Intel's spec is being used by other vendors like Xilinx, Altera and PLDA with slight modifications in LTSSM and power management states. However the basic Interface mentioned in Intel's spec is maintained by all vendors and so our design.

The main goal of Physical Layer is to establish the physical connection or channel for proper communication of transactions coming from above layer (Transaction Layer and Data Link Layer).

The main functions of Tx side of PHY layer are listed below

Link training through ordered sets TS1 & TS2

Insertion of SKP ordered sets every 1538 symbols for elastic buffer overflow/underflow management.

Sending Logical Idles in particular state of LTSSM and whenever there is no data available to send.

Sending ElOS (Electrical Idle) as dictated by ASPM and Software Power management.

Sending FTS(Fast Training Sequence) ordered sets whiling coming back to active state from Low power state.

Generation of PIPE signals which includes

Tx_data[32 or 16 bit]

D/K [4 or 2bit]

Tx_Elec_Idle

Tx_Compliance

Rate[1:0]

Width [1:0]

Pwr_dwn[2:0]

Reset_PhY

TxdetectRx

Insertion of STP, SDP, END kontrol characters (Implemented in DLL)

All the Data packets except Kontrol characters and ordered sets will pass through scrambler.

View PCIe Gen1/2 PHY full description to...

- see the entire PCIe Gen1/2 PHY datasheet

- get in contact with PCIe Gen1/2 PHY Supplier

Block Diagram of the PCIe Gen1/2 PHY IP Core

PCIe IP

- PCIe 5.0 Integrity and Data Encryption Security Module

- PCIe 6.1 Controller

- PCIe 5.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency

- 56G Serdes in 7nm bundled with PCie Gen 5 controller IP