PCIe Gen3 PHY - TSMC 28nm HPC/HPC+

* PCIe standard multi-lane interface

* PCIe power savings modes

* Port bifurcation support

View PCIe Gen3 PHY full description to...

- see the entire PCIe Gen3 PHY datasheet

- get in contact with PCIe Gen3 PHY Supplier

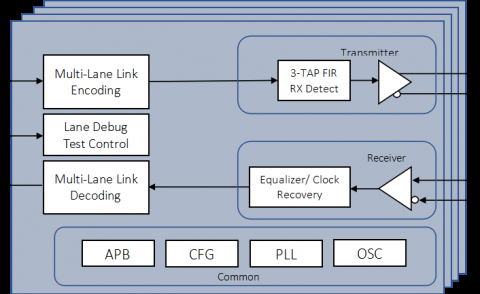

Block Diagram of the PCIe Gen3 PHY - TSMC 28nm HPC/HPC+

SerDes IP

- PCIe 5.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- Low-Latency SerDes PMA - 10GbE, 25GbE

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- 400G ultra low latency 56/112G FEC and SERDES IP sub 10ns latency

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency