Platform Manager Utility Function Core IP

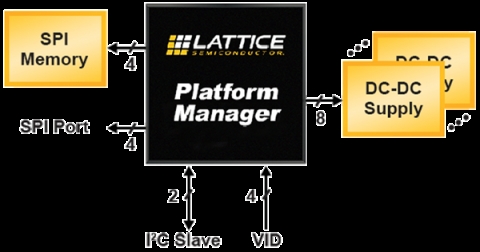

The Fault Logging function of this IP block supports the ability to log the Platform Manager’s analog and CPLD I/O states to an external flash memory device. Logic for logging and tracking multiple faults is supported, so that logged faults are not overwritten as a result of power cycling. The recorded faults may be accessed over a user SPI port provided for this purpose.

Enhanced closed-Loop trim expands on the on-chip hardware trim engine by providing the ability to set trim targets in real-time through either an I2C or SPI serial interface, as well as the new feature of being able to select individual channels for trimming operations. In addition, this IP function provides the option of supporting up to two VID trim channels, where up to 16 distinct trim targets can be dynamically selected through a 4-bit binary code.

The Lattice Platform Manager Core IP is widely parameterizable and supports a wide range of interface options, as well as importing configuration data from PAC-Designer.

View Platform Manager Utility Function Core IP full description to...

- see the entire Platform Manager Utility Function Core IP datasheet

- get in contact with Platform Manager Utility Function Core IP Supplier

Block Diagram of the Platform Manager Utility Function Core IP

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- Secure-IC's Securyzr(TM) AES-GCM Multi-Booster Réduire la liste des FPGA aux noms des gammes