Processor Core

The MD5 algorithm is an improved version of the MD4, created by Professor Ronald L. Rivest of MIT, and is closely modeled after that algorithm. It operates on message blocks of 512 bits for which a 128-bit (4 x 32-bit words) digest is produced. Corresponding 32-bit words of the digest from consecutive message blocks are added to each other to form the message of the whole message.

The MD5 core is a fully synchronous design and has been evaluated in a variety of technologies. It is available optimized for ASICs or FPGAs.

View Processor Core full description to...

- see the entire Processor Core datasheet

- get in contact with Processor Core Supplier

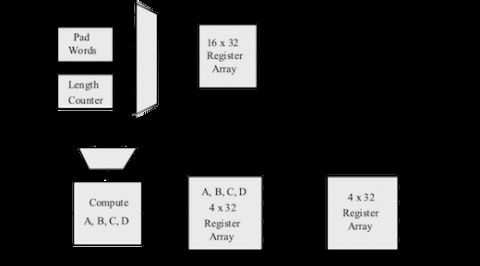

Block Diagram of the Processor Core IP Core

Processor Core IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- RT-660-FPGA DPA-Resistant Hardware Root-of-Trust Security Processor for Govt/Aero/Defense FIPS-140

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Secure-IC Securyzr(TM) Cyber Escort Unit IP provides real time detection of sero day attacks on processor

- 32-bit Embedded RISC-V Functional Safety Processor