Pulse Width Modulator

The core is designed for ease of use and integration and adheres to the industry's best-standards coding and verification practices. It provides access to its control and status registers via a 32-bit AMBA™ AHB or Wishbone slave port. APB, AXI4-Lite, or other interfaces can be made available on request. Technology mapping, timing closure, and scan insertion are trouble-free, as the core contains no multi-cycle or false paths and uses only rising-edge-triggered D-type flip-flops, and no tri-states.

View Pulse Width Modulator full description to...

- see the entire Pulse Width Modulator datasheet

- get in contact with Pulse Width Modulator Supplier

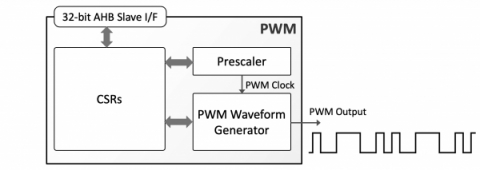

Block Diagram of the Pulse Width Modulator IP Core