Reed-Solomon Decoder

The codes are represented by the format RS(n,k) where n is the total number of s-bit wide symbols, and k is the number of s-bit wide information (data) symbols in a codeword. The Reed-Solomon Decoder performs detection and correction of encoded data available at the receiver after demodulation. The RS encoded data is then processed to determine whether any errors have occurred during transmission. Once the number of errors is determined, the decoder decides if they are within the range of correction. After determining this, the decoder corrects the errors in the received data

View Reed-Solomon Decoder full description to...

- see the entire Reed-Solomon Decoder datasheet

- get in contact with Reed-Solomon Decoder Supplier

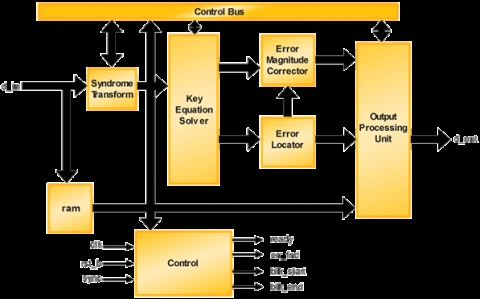

Block Diagram of the Reed-Solomon Decoder IP Core

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software